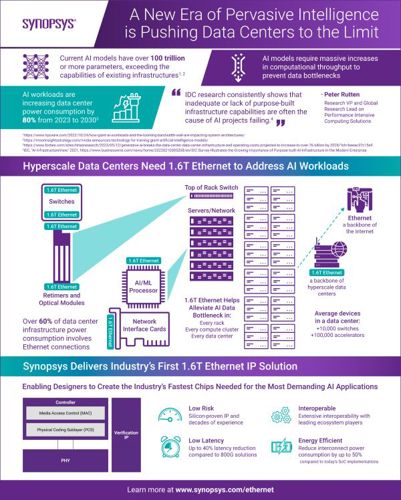

Hyperscale data centre require high-bandwidth, low-latency chips and interfaces to process petabytes of data quickly. Synopsys’ 1.6T ethernet IP solution will enable design teams to create faster chips for AI and data centre networking applications.

Synopsys’ announcement will enable hyperscale data centre providers, and the ecosystem that serves them, to future-proof their infrastructure using an extensive, interoperable, and proven IP portfolio.

With the growth in demand for high-speed data access pushing hyperscale cloud providers to upgrade their networking infrastructure Synopsys’ latest ethernet solutions will help chip designers and system architects reduce the design risks associated with developing the next generation of SoCs for cloud, AI, and 5G applications.

“With growing demands from large language modelling, HPC simulation, and AI training in hyperscale data centres, network boundaries are crossing over the Terabits per second threshold,” said Peter Jones, chairman, Ethernet Alliance. “The availability of development tools capable of meeting these needs is critical to the success of next-generation Ethernet standards addressing this market.”

“The massive compute demands of hyperscale data centres require significantly faster ethernet speeds to enable emerging AI workloads,” explained John Koeter, senior vice president of marketing and strategy for IP, Synopsys. “Our complete IP solution for 1.6T ethernet, pre-verified subsystems, successful ecosystem interoperability, and decades of expertise in developing and delivering the broadest interface IP portfolio will allow designers to confidently integrate the necessary functionality into their SoCs with less risk.”

Synopsys’ IP solution, including new 1.6T MAC and PCS Ethernet controllers, 224G Ethernet PHY IP, and verification IP, will help to accelerate time to market for AI and HPC networking chips.

The complete 1.6T ethernet IP solution optimises hyperscale data centre energy efficiency by reducing interconnect power consumption by up to 50% compared to existing SoC implementations. The new multi-channel, multi-rate Synopsys 1.6T ethernet MAC and PCS controllers decrease area by 50% and reduce latency by 40% by implementing a patented Reed-Solomon Forward Error Correction architecture, while helping ensure reliable data for Ethernet rates from 10G to 1.6T.

The silicon-proven 224G ethernet PHY IP can deliver robust link performance with exceptional signal integrity and seamless ecosystem interoperability for multiple channel lengths.