The NoC (Network on Chip) is the backbone of a chip that provides the interconnect infrastructure between the key processing elements. This new tool enables users to quickly find the optimal NoC configuration to reduce costs and speed up time to market, and according to the company, it is the fastest on the market due to innovative and intelligent algorithms.

According to the company this ‘try before you buy offer’ will enable engineers to see for themselves just how easy it is to design a NoC with its tool and hence the tagline - NoC in a SNAP. SignatureIP said that this its aim is empower the engineer to quickly experiment with different configurations of the SoC architecture and then simulate them in real time to measure throughput and latency so that they can optimise the design at the top level. The System Architect can then set the target Power, Performance, Areas and Timings into iNoCulator, which then creates possible topologies that can be easily and quickly tweaked to find the optimal solution.

Users simply have to tell the tool what they want, and it does all the hard routine work that used to take skilled engineers a long time.

In addition to the ‘Try Before You Buy’ offer, customers can also take out a subscription license on an annual basis that can be used for the interactive architectural exploration of any number of designs. It provides full access to all aspects of the tool and enables downloading the RTL of the final design for a fee per design download.

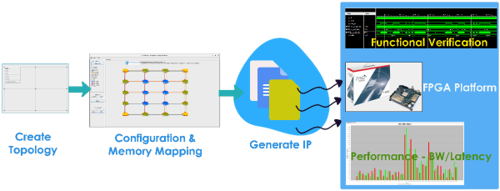

iNoCulator enables interactive whiteboard editing of the NoC topology through connection of initiators, routers and endpoints, and easy configuration. It supports on-the-fly instant simulation of bandwidth and latency, and estimation of power and area. iNoCulator provides pushbutton RTL generation with targets to an SoC design flow or to an FPGA emulation flow.

The iNoCulator EDA tool is processor agnostic so that it can be used with, for example, Arm or RISC-V processors and can connect many other on-chip IP blocks such as PCIe, CXL, and AI acceleration. This capability enables designers to create complex, high-performance heterogeneous SoCs that can support a wide range of applications.

SignatureIP has built in intelligent algorithms to automate and speed up many of the processes involved in scenario building that would have otherwise required manual configuration.

The tool can support non-coherent NoCs and can be configured as ring, mesh, concentrated mesh or torus topologies. It also has support for popular interface protocols (AXI, AHB, APB, SRAM) and multiple bus widths. The multiple clocking schemes include GALS, and the power control has power island generation and UPF output. It creates a layered, scalable physically-aware network.

At all stages, and especially during the initial trial, SignatureIP provides extensive support to help customers understand the full range of available features that enables the creation of an optimised NoC.