With an unlimited endurance (>5x1010), fast switching speed (210ps), and power consumption as low as 300pJ, the SOT-MRAM devices manufactured in a 300mm line are able to achieve the same or better performance as lab devices. This next-generation MRAM technology targets replacement of L1/L2 SRAM cache memories in high-performance computing applications.

SOT-MRAM has recently emerged as a non-volatile memory technology that promises a high endurance and low-power, sub-ns switching speed. As a result, it has the potential to overcome the limitations of spin-transfer torque MRAM (STT-MRAM) for L1/L2 SRAM cache memory replacement. So far, however, SOT-MRAM devices have only been demonstrated in the lab.

Imec has now for the first time proven full-scale integration of SOT-MRAM device modules on 300mm wafers using CMOS-compatible processes.

At the core of the SOT-MRAM device is a magnetic tunnel junction in which a thin dielectric layer is sandwiched between a magnetic fixed layer and a magnetic free layer. Similar as for STT-MRAM operation, writing of the memory is performed by switching the magnetization of this free magnetic layer, by means of a current. In STT-MRAM, this current is injected perpendicularly into the magnetic tunnel junction, and the read and write operation is performed through the same path – challenging the reliability of the device. In an SOT-MRAM device, on the contrary, switching of the free magnetic layer is done by injecting an in-plane current in an adjacent SOT layer – typically made of a heavy metal. Because of the current injection geometry, the read and write path are de-coupled, significantly improving the device endurance and read stability.

Imec has compared SOT and STT switching behaviour on one and the same device, fabricated on 300mm wafers. While switching speed during STT-MRAM operation was limited to 5ns, reliable switching down to 210ps was demonstrated during SOT-MRAM operation. The SOT-MRAM devices show unlimited endurance (>5x1010) and operation power as low as 300pJ. In these devices, the magnetic tunnel junction consists of a SOT/CoFeB/MgO/CoFeB/SAF perpendicularly magnetized stack, using beta-phase tungsten (W) for the SOT layer.

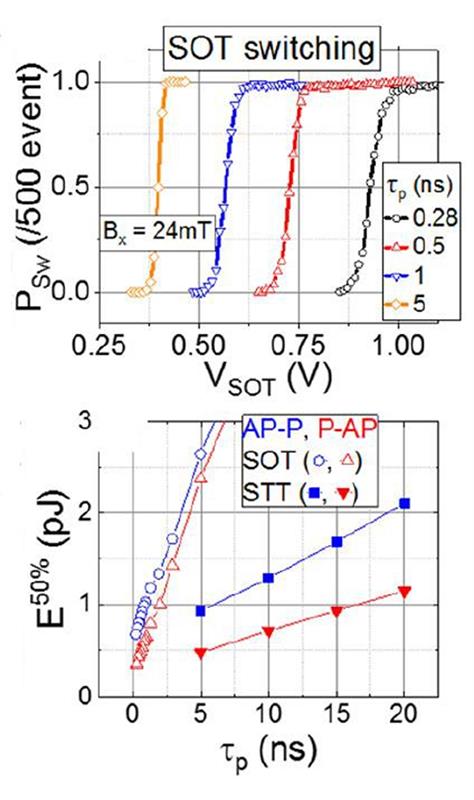

Above: Demonstration of SOT switching: (top) switching distribution as a function of pulse voltage for various pulse lengths; (bottom) energy vs. time showing ultrafast and low-power SOT device performances.

Above: Demonstration of SOT switching: (top) switching distribution as a function of pulse voltage for various pulse lengths; (bottom) energy vs. time showing ultrafast and low-power SOT device performances.

“STT-MRAM technology has a high potential to replace L3 cache memory in high-performance computing applications”, says Gouri Sankar Kar, Distinguished Member of Technical Staff at imec. “However, due to the challenging reliability and increased nergy at sub-ns switching speeds, they are unsuitable to replace the faster L1/L2 SRAM cache memories.

SOT-MRAM technology will help us to expand MRAM operation into the SRAM application domain. By moving this next-generation MRAM technology out of the lab, we have now demonstrated the maturity of the technology.”

Future work will focus on further reducing the energy consumption, by bringing down current density and by demonstrating field-free switching operation.

Imec’s research into advanced memory is performed in cooperation with imec’s key partners in its core CMOS programs including GlobalFoundries, Huawei, Micron, Qualcomm, Sony Semiconductor Solutions, TSMC and Western Digital.