Release 2018.12 features enhancements to the level of automation in Prototyping mode, plus the faster compilation of HDL to FPGA.

The HES-DVM provides design partitioning and partition interconnection tools designed to meet the growing need for FPGA prototyping; i.e. FPGAs used as a pre-silicon SoC verification vehicle to assure ultimate speed or as a hardware software co-verification platform.

Thanks to the use of virtual partitions, HES-DVM can also be used in the process of designing new prototyping boards to establish the most efficient board architecture for the project or with third party and in-house developed FPGA boards.

The 2018.12 release means that users will now be able to quickly evaluate various partitioning scenarios and choose the one which provides the best performance on a given prototyping board.

With this release, the productivity of an FPGA prototyping team is greatly boosted thanks to the addition of two new automation enhancements.

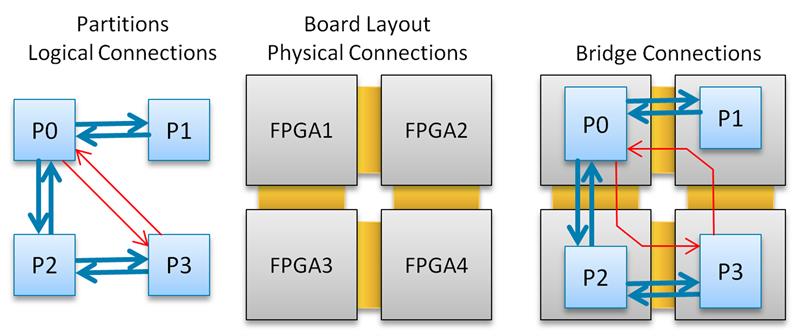

The first of these is Automatic Routing, which automatically resolves feed-through connections if there are no appropriate chip-to-chip traces on a prototyping board. The second is Automatic Physical Connections for multi-FPGA prototyping boards, which routes all inter-partition connections using available chip-to-chip traces and it intelligently assigns various types of I/O - including integrated serialization (SERDES) and differential signalling (LVDS).

In addition, and to further reduce the design setup turnaround time in HES-DVM’s Emulation and Prototyping modes, Aldec has developed a proprietary HDL compiler, details of which shall be announced later in the year.

“The latest release of HES-DVM boosts our FPGA Prototyping and Emulation solutions, through the addition of features that significantly shorten design setup time, enabling designers to evaluate more prototype scenarios than before in a given amount of time,” said Zibi Zalewski, General Manager of Hardware Division. “Users will also benefit from an ultra-fast turnaround time, from bug–fix to a revised prototype run, and potentially spare themselves from months of tedious work. Indeed, we are devoted to persistently raising the bar in FPGA-based emulation and prototyping technology.”