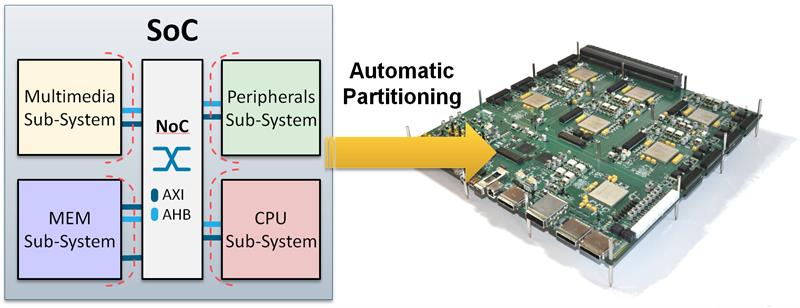

Due to design complexity and constraints, the manual partitioning of multiple FPGAs used for prototyping can take days, or even weeks, whereas the automation in HES-DVM can perform the task in minutes; ideal for exploratory, What-If scenarios.

The latest release of HES-DVM, 2019.09, features Aldec’s proprietary HDL compiler. Called SyntHESer, and launched earlier this year, in a recent in-house bench test, the compiler performed 10x faster than a leading standalone synthesis tool, when handling identical blocks of HDL for a circa 45-million-gate Deep Learning Accelerator (DLA) design.

“These additions to HES-DVM rise to some of the biggest challenges associated with the FPGA-based prototyping of an ASIC design,” said Zibi Zalewski, General Manager of Aldec’s Hardware Division. “With the 2019.09 release of HES-DVM, the most tedious and challenging activities, such as creating and matching partitions with on-board FPGAs or assigning limited FPGA I/O resources, are fully automated.”

For the 2019.09 release of HES-DVM, Aldec engineers designed and implemented fast and efficient algorithms capable of finding balanced partitions and minimizing required interconnections.

“The user can jump into the process of partitioning any time and modify the partitions and interconnections in harmony with automation algorithms,” adds Zalewski.

The HES-DVM also sees the introduction of Board Compiler, used to import files, in the form of Verilog structural descriptions, for third party boards that use Xilinx Virtex UltraScale devices. With this capability the user can easily reconfigure prototyping board by adding or removing inter-FPGA connections or creating hybrid configurations of tail (or daughter) boards and backplanes.

The 2019.09 software release of HES-DVM 2019.09 is available now