This is an extremely complex task given that automotive ICs, especially for advanced drivers assistance (ADAS) and autonomous driving systems, are employing increased levels of integration of highly complex and relatively new system functions. Thus, the most advanced automotive IC design teams are turning to high level synthesis (HLS) as the correct-by-construction first step in their design flows.

Two case studies recently released by Mentor, a Siemens business, profile the C++ methods employed by the IC design teams at STMicroelectronics’ Imaging Division and Bosch Visiontec. In both cases, their respective design teams were not only able to use Mentor’s ISO 26262 compliant Catapult HLS Platform to perform architectural exploration and converge on the right designs for their applications, they were also able to reduce the amount of time they would normally spend doing register transfer level (RTL) verification. This HLS-driven, correct-by-construction approach reduced the engineering hours, RTL licensing costs and time to market required for each project and enabled the teams to produce innovative, yet still ISO 26262 compliant chips faster.

The STMicroelectronics case study details how using this approach with the Catapult HLS Platform, their Imaging Division team quickly developed an image signal processing (ISP) device derivative for the automotive market and still meet the ISO 26262 requirements of the design.

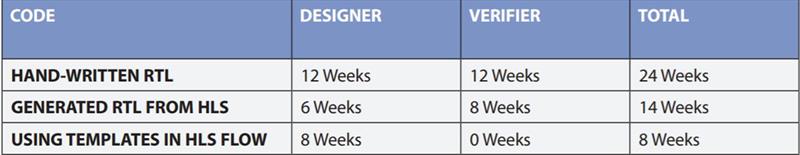

STMicroelectronics' Imaging Division, which has been using an HLS methodology since 2007, has developed an ingenious parameterised template/library system that helps the group reuse common functions described in C++. The major benefit of the HLS flow with templates is that it reduces development time and cost with no compromise in results and design quality (see Table 1). Using the flow, the team created the design 3X faster than hand-coding, and a single designer can perform verification, typically eliminating the need for a separate verifier resource.

Table 1: The benefits of the HLS flow

Table 1: The benefits of the HLS flow

In the case of Bosch Visiontec, the team used an initial Matlab model to write synthesisable C++ based on its automotive vision SoC specification. It then created parameterised functions across multiple designs. Each of the algorithms evolved during the development stage. By using Catapult HLS, the team simply changed constraints in the tool and re-ran the design flow to examine the results. This allowed them to validate the algorithms and see the effects on area and performance. The team also could explore micro-architecture changes without changing the C++ code. In addition, the team modified the clock frequency and synthesised the C++ code using Catapult without a change in the directives to meet the post-synthesis timing specification. This allowed them to converge on the right architecture for their design.

Then to catch bugs prior to synthesis, the team employed Catapult Property Checking (CPC), which cut weeks off verification debugging time, as CPC identifies and formally proves hard to find issues like uninitialized memory reads and divide-by-zero violations. The team then used the SCVerify flow within the Catapult HLS Platform to automatically generate the infrastructure for verifying the functionality of the Catapult-generated RTL against the source code, and they reused the original C++ testbench. This eliminated further verification cycles that would have been required if they had started with the older, traditional RTL-coding approach.