Transistors have been miniaturised for the past 50 years based on Moore's law. But we've now reached the point where transistors can't continue to be scaled any further.

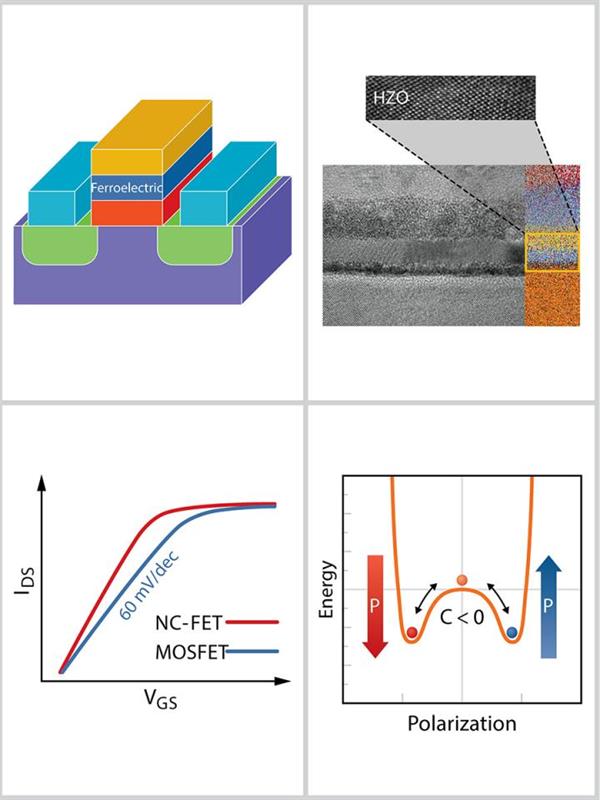

In the journal Applied Physics Letters, from AIP Publishing, researchers review negative capacitance field-effect transistors (NC-FETs), a new device concept that suggests traditional transistors can be made much more efficient by adding a thin layer of ferroelectric material. If it works, the same chip could compute far more, yet require less frequent charging of its battery.

The physics of the technology are being assessed throughout the world and, in their article, the researchers summarise state-of-the-art work with NC FETs and the need for self-consistent and coherent interpretation of a variety of experiments being reported in the literature.

The concept of NC-FETs is intriguing because not only does it address a pressing problem of finding a new electronic switch for the semiconductor industry, but also because it serves as a conceptual framework for a broad class of phase-transition devices collectively termed "Landau switches."

Although hundreds of papers have been published on the topic, according to the researchers, the validity of quasi-static NC and the frequency-reliability limits of NC-FET are still being hotly debated.

If conclusively demonstrated and integrated into modern ICs, the impact of the NC-FET transistors will be transformative.

"Given the potential, there is a need for systematic analysis of the device concept," explained co-author, Professor Peide Ye. "We found that the data from various groups has a wide scatter and researchers are using very different techniques to characterise their devices. This requires an integrated and comprehensive analysis of the existing data set."

The researchers hope their work will bring the community together to suggest ways of making coordinated progress toward realising this promising technology.

| This is a schematic image of a NC-FET where a CMOS-compatible ferroelectric HZO layer is part of the gate stack to realize negative capacitance in the gate stack and sub-60 mV/dec transistor operation. Image credit: Peide D. Ye |