This new paradigm comes in the form of the eclipse-based tool SDSoC Design Environment which enables the development of the SoC using only a software environment and using a high-level language like C or C++. This tool – via a combination of High Level Synthesis and a software defined connectivity framework – connects the results of the HLS into the software application. Such an approach enables the design team to move functions between the processor and the programmable logic with the click of a button. Of course, when users move functionality to the programmable logic they also gain a significant performance increase which comes naturally with the use of the programmable logic.

Within the SDSoC environment, they can alse use several different operating systems on the processors from Linux to FreeRTOS and, of course, a bare metal approach.

Development flow

Developing a Zynq system within the SDSoC environment requires a platform definition split into two sections:

If users do not want to define a platform, they can use a pre-defined development board such as the ZedBoard, Zybo or Zc702.

With the platform selected, the development flow allows developers to:

1.Develop the application in our high-level language

2.Analyse the design using provided performance monitors to determine bottlenecks in performance

3.Accelerate the bottleneck functions into the programmable logic using the SDSoC project overview

4.Re-validate the performance and, if necessary, select other functions to be accelerated as well.

To obtain the best performance in the programmable logic, users may need to define some optimisation pragmas within the function to be accelerated, so that they can define what optimisations the HLS tool performs. As SDSoC is also aware of the available clocks and their frequencies, they can control both the frequency of the data motion network which transfers data to and from the accelerated cores and the frequency of the cores themselves.

Library support

To enable faster development of the end application, SDSoC comes with several HLS libraries which the developers can use in their applications. There are several libraries and stacks which can be used as part of the development. These include:

As these libraries have been developed to support HLS, they provide the development team with a considerable boost as they do not need to develop similar functions.

Real world example

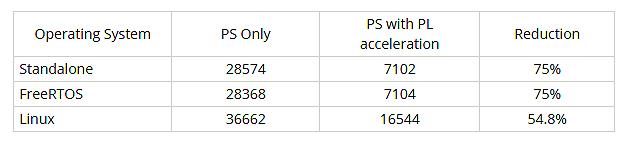

To demonstrate the benefits gained by acceleration and the impact of the operating system selected, an Advanced Encryption Standard (AES) example was developed. AES is commonly used in embedded systems to protect data within a system or data which is entering or leaving the system. AES is also a good example of an algorithm which is described at a high level, but best implemented in programmable logic fabric. The developed AES 256 application was targeted at each of the three operating systems supported by SDSoC, first running only in the processor system and then in the programmable logic.

Figure 2 - AES Acceleration results for different SDSoC operating systems

Debugging and optimising performance

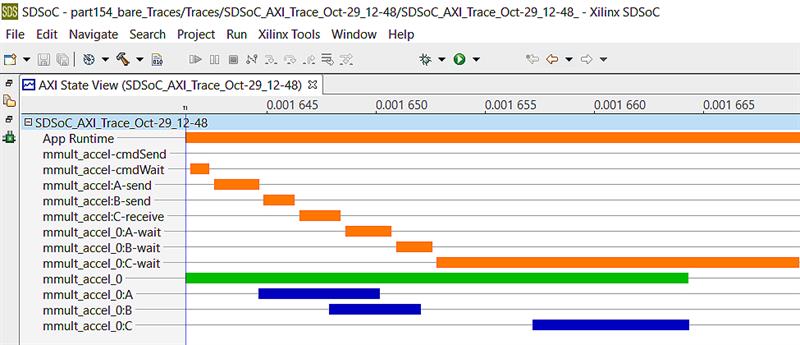

Within the SDSoC development environment, developers can use traditional software debugging techniques such as the insertion and exploitation of breakpoints along with examining memory and register contents. Once identified functions have been accelerated, there are instances where developers need to understand the further interaction between processor and programmable logic. SDSoC provides two methods the developers can use to fine-tune their application: AXI profiling and tracing - both options are instrumental to the design and provide additional hardware functionality to the programmable logic. Profiling provides high level information on the interaction between the processor and the programmable logic, while tracing is more in-depth and enables developers to see considerable detail regarding the hardware/software interaction.

Figure 3 - Results of tracing an example application (orange = software, green = accelerated function and blue = transfer)

Conclusion

SDSoC enables the development of all programmable SoCs using a high-level language, with the functional partitioning between the processor and the programmable logic able to be optimised once the application functionality has been developed and prototyped using the processor.

With several HLS-ready libraries provided to use in the development of the application, these can reduce the development time while still benefiting from the ability to accelerate functions in the design with ease.

Author profiles

Nick Ni is senior product manager of SDSoC and Embedded Vision at Xilinx, and Adam Taylor is an embedded systems consultant at Xilinx.