Metasimulator runs 100 times faster than Monte Carlo analyses

The High Sigma Monte Carlo (HSMC) metasimulator from Solido Design Automation is said to provide accurate, scalable and verifiable analysis and design solutions for memory chips. The developer adds the package is at least 100 times faster than Monte Carlo analyses.

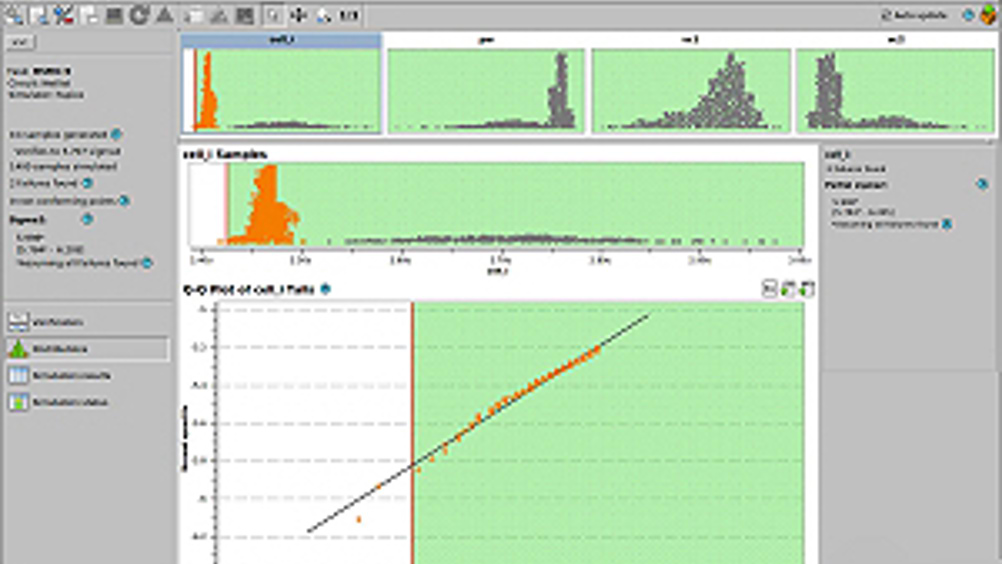

HSMC provides rapid analysis of the yield and performance trade offs for memory design. Achieving high-sigma memory verification in thousands, rather than millions or billions, of simulations, it analyses the Monte Carlo samples, then focuses its SPICE simulation resources either to find rare failures or to validate the target yield. According to Solido, an HSMC run using 5bn Monte Carlo samples run can take as little as 15 minutes.

HSMC interfaces to all leading SPICE simulators and runs at the command line, while supporting parallelisation to many cores and/or machines. It analyses design sensitivities to variation, presenting design opportunities to shrink memory area, power and improve performance, as well as providing integrated results verification.