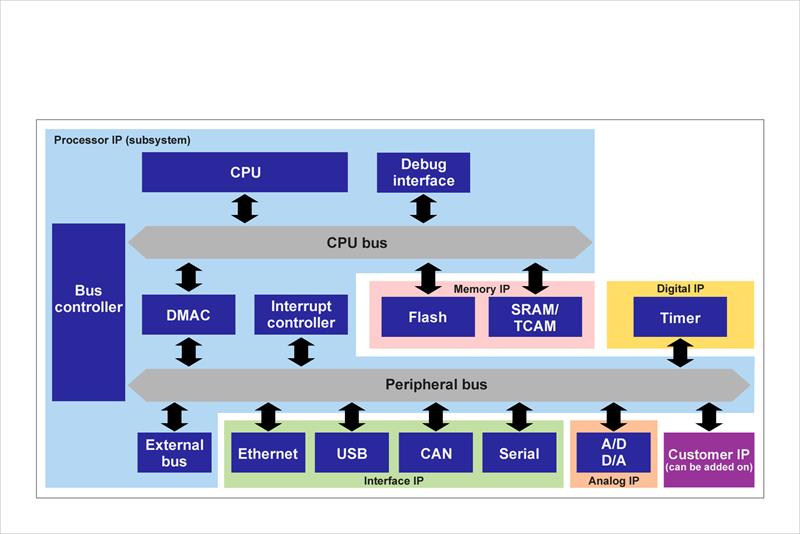

Renesas has incorporated a selection of IP into its microcontrollers (MCUs) and system on chip (SoC) products spans, including central processing unit (CPU) IP, communication interface IP, timer IP, memory IP, and analogue IP.

The first batch of offerings will consist of over 40 licenses, including CPU cores (RX, SH, etc.), timer IP for motor applications, USB cores, and SRAM. More licenses will be offered moving forward in response to demand.

Manufacturers interested in developing custom chips for applications such as AI, autonomous vehicles and robots can leverage Renesas IP in their subsystems design, allowing them to concentrate on developing their own competitive IP assets, and thereby speeding up the advanced semiconductor development process.

In addition, manufacturers using FPGA devices for early development can utilise Renesas IP assets to speed up software development, allowing for early evaluation and accelerated time to market, and then transition immediately to mass production. On the other hand, customers who prefer to use existing software assets can continue to utilise Renesas IP assets, thereby reducing the labour needed to develop, verify, and evaluate software and boards, and allowing for more efficient system development.

Previously, Renesas provided IP assets to select customers. The new effort to expand IP sales marks Renesas’ entry to the IP licensing market, which is growing at a rate of over 10 percent a year and is expected to be worth around a trillion yen in 2025. Renesas aims to achieve sales of more than ten billion yen in 2025.

Moving forward, Renesas intends to capture and expand growth in the IP market by offering customers the ability to customise their IP, as well as by licensing existing IP assets.