While that handled problems at the high performance end of the spectrum, the emergence of the IoT has posed a new set of challenges; creating devices that can work for maybe a decade powered only by a small battery or even by energy harvested from the environment.

It is fairly evident that such needs cannot be met by the vast majority of commercially available parts and this has seen the emergence of companies looking to take advantage of so called sub threshold processing. This technique allows a microcontroller, for example, to run from a voltage supply lower than the transistor’s switching voltage.

One company targeting this market is Ambiq, which recently launched Apollo 2, its second generation sub threshold processor.

Founder and CTO Scott Hansen said: “People have been using technology designed for other things. We believed we had to start from scratch. We have redesigned the system and achieved dramatic savings.”

The theory behind sub threshold processing is seemingly simple – power consumption is a function of V2; when the operating voltage decreases, the amount of power consumed drops significantly. But as the operating voltage drops, so too does performance. Whilst that might be a problem in a laptop computer, it may not be a problem for an IoT edge device.

Hansen continued: “Instead of swinging from 0 to 1.8V, we’re swinging from 0 to 0.5V. Because we never turn the transistors full on, we get big power savings.”

Compared to what Hansen calls a typical circuit operating at 1.8V, a ‘near threshold’ circuit operating at 0.5V can reduce dynamic power consumption by up to 13 times. A ‘sub threshold’ circuit operating at 0.3V could reduce dynamic power by up to 36 times.

Hansen contends that textbooks say sub threshold processing isn’t possible. “So people don’t know about it. But it comes with a problem: most circuits will fail at low voltage – and that’s something we’re good at solving.” Its solution is SPOT – sub threshold power optimised technology. This deploys dynamic, adaptive strategies that keep the circuits operating optimally.

Ambiq was launched in 2010 and its first product was a real time clock chip. “We then built Apollo, which has had design wins in wearables and smart home apps.”

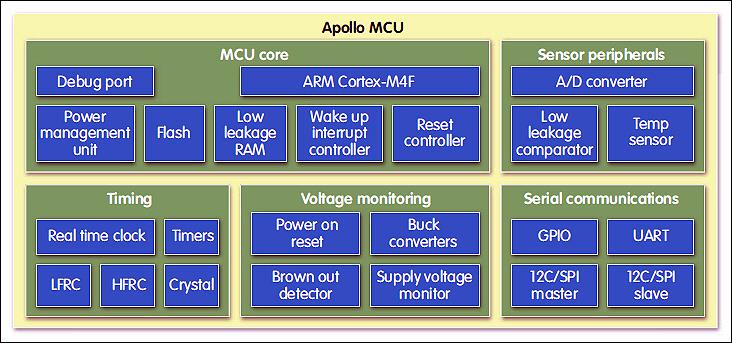

Block diagram of Ambiq's Apollo 2 microcontroller

Lauri Koskinen, co founder and CTO of Finnish company Minima Processor, has been working on sub threshold processing since 2008. “Minima came out of two university research programmes,” he said, “as well as from Finnish research centre VTT. We thought of some new ideas, made a few test chips, then started to think about the business potential.”

Koskinen said Minima is looking to improve energy efficiency. “And low voltage is the means to achieve this. While it’s not difficult to get a single processor to run at low voltage, the main problem is robustness – getting suitable yields is the hard part.”

He said most systems today are battery operated. “Batteries are energy storage devices,” he continued. “When you drop the operating voltage, system performance drops and so does energy consumption.”

One of the major issues with operating at sub threshold voltages is process variance. “But such devices are also subject to the effects of ambient temperatures.”

So how does Minima get processors to work at sub threshold voltages? “There are companies doing sub threshold who do a lot of work on the semiconductor process side, developing new cell libraries,” Koskinen said. “We modify the device’s clocking so that it becomes adaptive, but the processor remains synchronous. It’s much the same as an electronic stability system in a car; special sensors within the logic look pre-emptively at different points and slow the system if it’s going too fast.

“It’s a hardware and software approach. Although the hardware can work by itself, the software comes into play when it comes to yield. The software is also compatible with dynamic voltage and frequency scaling systems; that’s something we haven’t seen from competitors.”

Rather than designing its own processor, Minima is working with a range of companies. “We’re process and IP agnostic,” he noted, “so we’re not limited to microprocessors. We could also work with DSPs, for example. We’re also looking closely at the RISC-V architecture and are developing our own RISC-V IP.”

Minima says it’s in the design phase with its lead customer and expects to see its technology in a product in 2017. “We’ll probably see it used in things like ‘always on’ circuits, including always on audio, as well as touchscreens.”

Koskinen believes that on a 40nm process, Minima’s technology will bring an energy consumption benefit of up to x14 when a device is running from a 0.3V supply.

Ambiq, meanwhile, has built its Apollo range on the Cortex-M4 core. The latest device, Apollo 2, has a 16k cache and can run at up to 48MHz. “Apollo 1 didn’t have a cache,” Hansen said. “That’s not possible at 48MHz. Apollo 2 also has quite a few power domains and uses less than 10µA/MHz.”

There is a road map for the Apollo range, Hansen said. “We need to offer four things: computation; connectivity; sensing and actuation; and power management. We intend to offer all these in time.

“Next year,” he concluded, “We will see lower energy consumption and higher frequencies. Extrapolating, I think users will be able to run Android on a sub threshold processor.”

Is negative capacitance the way forward? One of the potential approaches is negative capacitance and this was addressed by the FERN – ferroelectrics for nanoelectronics – project, involving Newcastle University and Imperial College. The work was led by Anthony O'Neill, Siemens Professor of microelectronics at Newcastle. Talking to New Electronics in 2010, he noted: “There has been experimental evidence that effective negative capacitance can be seen in ultra thin ferroelectric films. If such material could be incorporated into a transistor, then it would be able to reduce the voltage needed to switch a transistor between its on and off states.” Prof O’Neill published a paper in 2014, outlining work which detected negative capacitance at room temperature in materials suitable for integration into CMOS technology. Speaking to New Electronics early in 2017, Prof O’Neill said: “There has been a good deal of interest in our work and some researchers claim to have made transistors exhibiting negative capacitance. However, I am not aware of any company able to make devices that incorporate negative capacitance.” Professor Chenming Hu from UC Berkeley is also interested in negative capacitance. Speaking to the Synopsys User Group in 2016, he said the industry needed to overcome Boltzmann’s 60mV/decade switching limitation. If this slope can be made steeper, the threshold voltage can be reduced. “Negative capacitance transistors are a ‘promising direction’,” he noted. Prof Hu said Berkeley has demonstrated so called NC-FETs made on a 30nm process and featuring a 5nm layer of the ferroelectric HfZrO2. “These break the 60mV/decade limit,” he contended. |