There is always an issue to be found and it’s true to say that some applications are particularly sensitive to them.

In addition, test is a significant component of the recurring cost of a product and directly impacts on the profitability of a design. The expense of testers and the time spent testing each die will contribute significantly to the final cost of a product.

Finally, test is also a consideration in winning sockets. The better the quality of the samples delivered for prototype evaluation, the more likely the design of the product will be successful, with the caveat that test development time should not impact the delivery schedule.

Compared to digital design, one of the big differences in the design methodology is how test is addressed by analogue designers. Digital designers have tools to automatically include testability into their designs. This allows them to generate test patterns and assess the test coverage and implications on the additional area overhead. These tools are based on the concept of faults. By injecting faults, the ability of test to identify failures can be analysed and coverage reported. Coverage is the percentage of failures that the test can identify. For digital designers, the concept of faults - stuck-at-low, stuck-at-high, and traditional fault model - are sufficient to enable the automation of test.

Analogue testing

Traditionally, analogue testing has focused on the functionality and parametric performance of the die such that the circuit operates as it was designed. As a result, it has been a challenge for designers to apply the concept of faults to analogue design. Faults need to be defined for each macroscopic characteristic of the design - for example, the open loop gain fault, the offset voltage fault, and so forth.

Defining the faults and the failure modes for analogue circuits has proven challenging and difficult to correlate to DPPM. An alternative approach has been proposed, called defect-oriented test simulation. Instead of trying to define faults for every circuit characteristic, the approach focuses on defects.

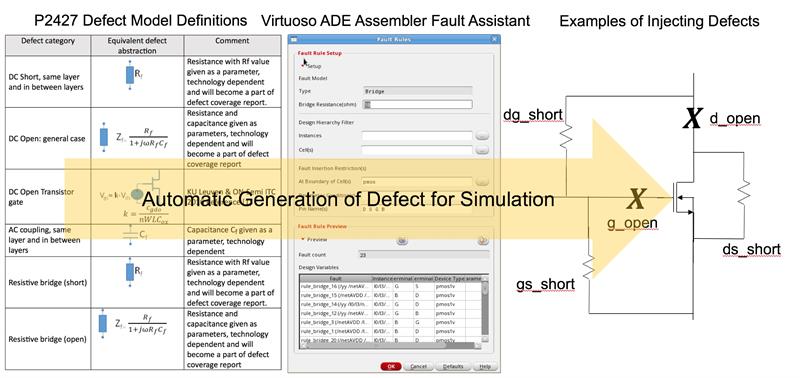

Figure 1: Generating defects for simulation |

Defects may be due to issues in the manufacturing process – for example, incomplete etching of the metal that results in shorts between two adjacent metal interconnect lines going over a step.

Defect-oriented testing targets such anomalies in the circuit structure while applying the stimuli, observes their effects on circuit characteristics and assesses the number of defects in the structure that may become detected during production test.

As such, defect-oriented testing does not necessarily replace existing specification-based test. It is rather seen as a means to quantify the effectiveness of a certain test and provide information as to whether action needs to be taken to improve the test quality.

As this methodology has matured, an IEEE P2427 working group has been launched to define a standard for modelling manufacturing defects for simulation.

Standardising the models for defects has allowed development of tools to perform the simulation with defects, so that analogue designers now can have a tool to simulate production test set-up and evaluate its effectiveness.

Defects are modelled as low-valued resistors for shorts and high-valued impedances for opens.

Figure 1 illustrates how this simulation methodology has been realised in the Cadence Legato Reliability Solution.

Using the fault assistant in the Cadence Virtuoso ADE Assembler, the defect models have been converted into rules. The rules are used to define where the defects are injected into the circuit. The Virtuoso ADE Assembler generates a list that can be used by the Cadence Spectre Accelerated Parallel Simulator to perform defect simulation.

Each defect is simulated, and the simulation results are compared to the test limits to determine whether the test identifies a defect.

To better understand the how to simulate analogue test, let’s look at an example.

The device under test is a bandgap reference. The first point to keep in mind is that the production test is being simulated. The testbench is based on the load board used in the tester and the test stimulus.

The production test programme consists of five tests:

1. IDDQ, the quiescent power supply current

2. Vout, the bandgap reference output voltage

3. Rout, the output resistance of the bandgap reference

4. PSRR, the power supply rejection of the output voltage

5. Delta Isupply, the change of the power supply current with power supply voltageº

After creating the testbench, setting up the tests, and defining the measurements, the next step in the process is to use the Fault Assistant to define the rules for identifying the defects to be simulated.

For the device under test, we will look for the defects caused by device failures due to junction shorts.

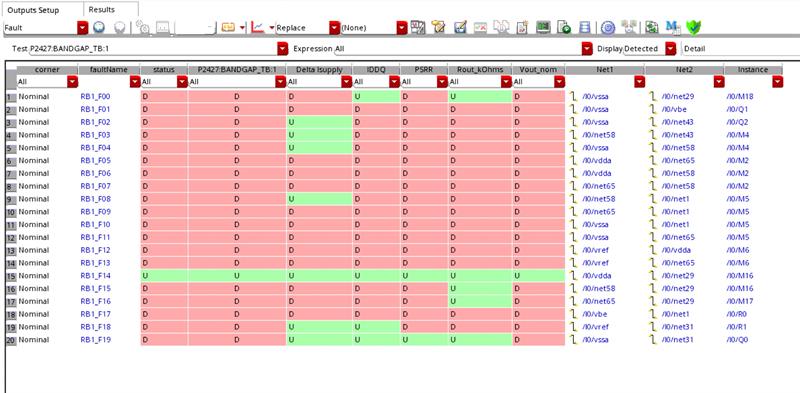

Shown in Figure 2 are the simulation results for the device defects. The test coverage for the test program is high; however, the test misses one defect – namely fault “RB1_F11” in the picture above.

The reason that this defect is not found by the test is that the defect is in the start-up circuit and all the tests are performed on the circuit during normal operation, that is, after the start-up circuit has turned off.

Figure 2: Defect simulation test results |

Since the start-up circuit is not active when the tests are performed, it is not found. To achieve 100% test coverage, a new test would need to add a test that measures the circuit during start-up.

Here we have looked at the challenges to consider in the testability of analogue designs, and the significant progress that’s been made in the methodology for simulating analogue test.

Using a simple example of using defect-oriented test to simulate a production test, in order to calculate the test coverage, we’ve been able to demonstrate how a new flow allows analogue designers to evaluate the test program along with the testability of the design early in the design flow resulting in shortened test times – and thus translating into reduced production costs.