So if you’re designing such systems, what tools are available to help you minimise power consumption? The answer is a wide range – everything from laying out PCBs in a more power efficient manner to tools which help you design at the RTL level.

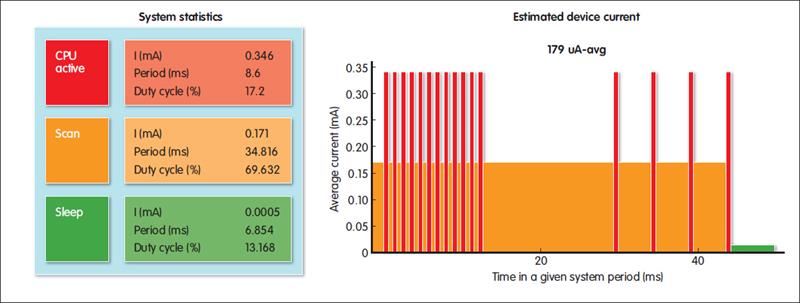

Perhaps the simplest way of working out how much power your system will draw is to start with the microcontroller at its heart. Adrian Valenzuela, Texas Instruments’ director of processor marketing, said the data from the company’s power estimation tool is useful in two ways. “Firstly, it can help to set the energy budget; can you do what you want to achieve? Secondly, it helps you to determine what kind of power supply you might need.”

TI’s Power Estimator has been available for a decade and is processor specific. “But it does present users with the same view of peripherals and the various power modes available,” he added.

However, while the tool doesn’t focus on application software, it can give a view of duty cycles. “From a power optimisation point of view,” Valenzuela said, “customers aren’t always aware of which power states are available. By showing the available modes, users can see the power impact.”

There’s always the possibility of using your PCB design package to help with power consumption. David Haboud, technical marketing engineer with Altium, noted: “As the focus shifts towards more wireless communication, power demands increase and available board space decreases. Innovative technology use more components, each with their own power requirements. Elements such as length tuning help to deliver power efficiently to these components.”

Haboud also points to the better design of power and ground copper areas. “This allows designers to distribute their power properly. Being able to have all power components on the same layer allows for a more compact design. Increased signal integrity from length tuning optimises power consumption by diminishing power-noise sources and current leaks.”

While good PCB design might not be an obvious way of dealing with power demands, Haboud explains why. “Streamlining the PCB design should result in cleaner code. Designers can then use Tasking embedded software development tools to optimise code size and execution time. This should enable a less power hungry processor to be selected and a smaller flash memory. Shorter execution times mean further savings can be made by cutting the operating frequency or putting the system into sleep mode for longer.”

Embedded software development tools provide an area on which all designers can focus. Part of this area – power debugging – allows power to be correlated against the software’s execution flow.

It’s a function included in IAR Systems’ Embedded Workbench and the company says that, by coupling source code to power consumption, applications can be tuned. But it notes the approach is based on close integration of current measurement and trace probe and this can be done by powering the target system through a debug probe (see pic 1 below).

It notes the voltage drop across a small resistor can be measured by a differential amplifier and then sampled by an A/D converter. Integration is ‘very close’, it claims, ‘and the accuracy should be good’.

Thomas Sporrong, IAR’s global FAE manager, commented: “IAR Embedded Workbench incorporates a technology for power debugging which enables engineers to measure and optimise their applications’ power consumption during their daily code and debug cycle. Power samples are visualised together with interrupt activity and other events on a shared timeline, giving a quick understanding of how code and power consumption correlate. In combination with the compiler’s speed optimisation, this technology helps code to be optimised on every level.”

One area where power is often wasted, says IAR, is by peripherals not being controlled strictly enough. “If you are designing for low power,” it notes, “it is vital you disable peripherals, not leave them unattended when they are not in use.”

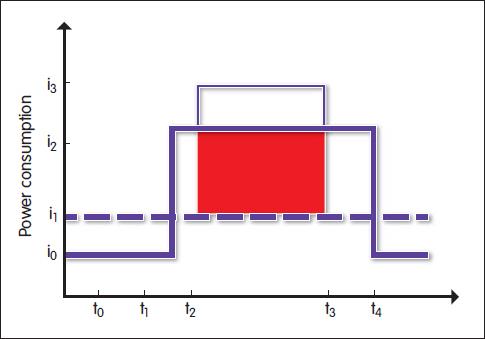

The company gives the example of a system in which an analogue comparator’s operation is suspended by a higher priority task. Ideally, it says, the comparator should be turned off when the task is suspended, then re-enabled, minimising power consumption.

|

In fig 2, the system is inactive at t0. When the system is activated at t1, the comparator is started and current rises to i2. At t2, the higher priority task suspends the comparator. Not only is the comparator not turned off, more peripherals are activated by the new task, increasing current to i3. At t3, control is handed back to the lower priority task, which completes at t4. The red area in fig 2 shows the amount of power that could have been saved, had the comparator been turned off.

More complex systems require more complex approaches, particularly if the design includes a custom part. Jon McDonald, technical marketing engineer with Mentor Graphics, said the company had tools ranging from RTL power estimation to those for detailed analysis. “We have an approach based on estimating dynamic power consumption based on system activity. At the high level, this can also run software and realistic workloads, but it involves significant amounts of data processing.

“We are always telling software engineers to write more power efficient code,” he continued. “If you can run software on a virtual platform, you can see where power is used and take different approaches to see if power consumption changes.”

Embedded engineer Arvind Raghuraman noted the symbiotic relationship between hardware and software. “Hardware provides the facilities, software takes advantage of them.” Optimising those hardware features can be achieved using the operating system. “Nucleus has a power management framework,” he pointed out, “but you won’t know power consumption because you haven’t run the software. There’s a set of APIs that enable power management decisions, such as throttling the CPU, but some decisions aren’t straightforward.”

Frank Schirrmeister, director of product management and marketing with Cadence’s System and Verification Group, said virtual platforms can be used to annotate the power consumption of the system underneath. “High level synthesis techniques have also evolved which can be used to generate different implementation options for optimising power.”

He also noted that SoC designers can import data from Cadence’s Incisive and Palladium systems into its Joules program to get early system level power analysis.

Andrew Caples, senior embedded product marketing manager with Mentor Graphics, noted that developers don’t need to worry about low level design. “They can write to an API, say ‘shift the frequency’ and see all of that handled by our framework.

“We are seeing the implementation of very power efficient designs, but this requires low level implementation. However, developers can write power efficient code, measure power consumption as they’re developing and make the necessary changes.”

Fig 2: Analysis tools can show where power can be saved by turning peripherals off when they are not active.

Fig 2: Analysis tools can show where power can be saved by turning peripherals off when they are not active.