Last month Cadence unveiled the latest version of its Virtuoso Platform in a move intended to support enhanced system design and simulation layout. Not only that, it has been enhanced to better support the development of advanced nodes from 22nm down to 5nm.

According to Yuval Shay, Product Management Director, Analog/Custom IC Group, Cadence: “What we have announced is a significant upgrade to the Virtuoso Platform. I don’t think there’s a single application that we haven’t upgraded or made significant changes to.”

The enhancements affect almost every Virtuoso product, providing system engineers with an environment and ecosystem that will enable them to design, implement and analyse complex chips, packages, boards and systems.

“The engineering community needs EDA tools that are able to provide them with the ability to efficiently design, test and layout circuits that not only address the issue of reliability but do so without impacting on a designer’s productivity,” Shay explains.

Some of the big challenges facing EDA today include its ability to handle shrinking device/process size and to manufacture those advanced nodes as well as the impact of multi-technology designs and model support of devices and multi-technology simulation.

As Shay suggests, “Today, design teams need to be able to easily and quickly prototype designs and that requires much more agile editing in order to work quickly through design optimisations that use manufacture-able parts and processes that can be controlled.”

The latest version of the Virtuoso Platform is a response to that, but is also looking to address one of the biggest challenges confronting companies today.

“Traditional system companies that in the past would not have attempted to design an IC or use Virtuoso, or had a team that specialised in analogue design, are becoming more vertically integrated. As a result they are taking a much more system approach when it comes to bringing products to market.

“Likewise, our traditional customers, i.e. semiconductor companies, are developing more integrated solutions and are looking to provide their customers with systems either in the package or on the board – it’s no longer simply about IC design, but system design.

“The level of integration that we are seeing is extremely high, and Virtuoso looks to address this trend,” Shay says.

Tackling integration

“The latest version of the Virtuoso Platform now allows system engineers to edit and analyse the most complex heterogeneous systems seamlessly,” according to Shay. “More importantly, it enables package, photonics, IC analogue and RF engineers to work through a single platform and make use of the the full breadth of the platform’s design applications.”

Shay explains that at the heart of the new system’s design environment is a set of technologies that enable simultaneous edits across multiple process design kits and technologies.

“The platform has also been designed to provide seamless interoperability with Cadence’s SIP Layout and the Sigrity analysis technology portfolio for a comprehensive chip-to-board toolset.”

According to Shay: “One of the big challenges confronting design teams is dividing layout tasks. Virtuoso now features a concurrent real-time team design editing capability, which allows teams to distribute layout tasks and perform what-if explorations. This is particularly useful for design-rule check (DRC) fixing, chip finishing and manual routing.”

While every design will be different, Shay takes the example of LIDAR to demonstrate how this platform will benefit, in this case, designers working in the automotive space.

“Lidar is the laser equivalent of radar and works by sending out laser pulses and then timing when they return. By doing that, it is possible to build up a picture of what is surrounding the vehicle,” Shay explains.

But Shay makes the point that at present, “it simply costs too much to install economically in vehicles. Estimates vary, but if each vehicle needs, say, 15 of these devices the costs are prohibitive.

“LIDAR is very mechanical and expensive; we need to see an integrated solid-state solution that costs under $100, and while it’s going that way, it’s clear that it remains at a price point that is unsupportable in all but the most expensive vehicles.”

If the cost of LIDAR is to be reduced, then the way it is made has to be cheaper and that means using solid-state laser diodes, MEMS mirrors to direct the light, silicon photonic detectors, and substituting high-precision optics with lots of digital signal processing.

According to Shay that would require a LIDAR that incorporates a laser-diode transmitter, with MEMS mirrors, a super-sensitive SPAD detector (single photon avalanche diode), and signal processing that is capable of pulling the whole system together.

“There are several different technologies that need to be packaged together,” he says, “and in order to achieve that, design engineers need a system that can handle all of these technologies not just one at a time, but in the context of the packaging, and the other die.

“Throw in Artificial Intelligence and neural networking to look at and process an image, and all of this will take integration and a lot of products.”

Crucially, there is full interoperability between Virtuoso (layout), Allegro (PCB and packaging layout), and Sigrity (signal and power integrity) providing the support necessary for mixed technologies such as MEMS, photonics, power devices, RF, as well as mainstream analogue and digital silicon.

| Above: Virtuoso now incorporates innovative advanced-node methodologies to speed the designs done in process technologies from 22nm down to 5nm |

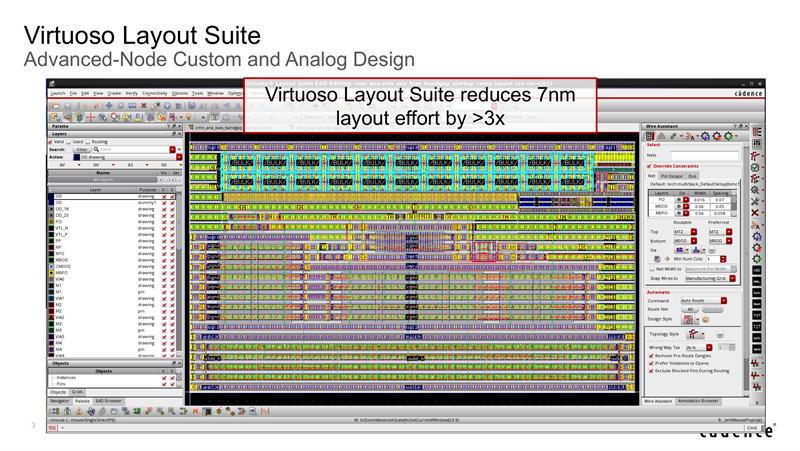

Advanced nodes

In this release of the Virtuoso platform, Cadence has also incorporated innovative advanced-node methodologies that speed the designs done in process technologies from 22nm down to 5nm.

“Many companies are using these advanced nodes, many more than we anticipated,” says Shay.

“While there’s demand for older nodes we need to provide a solution for 5nm designs; there are more than 170 companies developing in advanced nodes – the growth has been amazing. In automotive for example, we are seeing products using 16nm and 7nm.”

By collaborating with leading-edge foundries, ecosystem partners and customers, Cadence has been able to develop advanced technologies that are able to automatically manage process complexities with innovative methodologies that allow engineers to focus on their designs.

In circuit design and analysis, advanced statistical algorithms specifically targeting FinFET designs are able to uncover circuit variances early on in the design process, reducing design variation analysis time by as much as 20% using advanced statistical algorithms.

In layout design, a unique multi-grid system abstracts complex design rules of the latest 7nm and 5nm processes, while allowing engineers to increase their use of placement and routing technologies to significantly increase their layout design productivity.

“The Virtuoso Layout environment is evolving from an electrically aware layout to the industry’s first electrically and simulation-driven layout using unique sets of in-design technologies to ensure circuit integrity and performance,” Shay suggests.

| “The engineering community need EDA tools that are able to provide them with the ability to efficiently design, test and layout circuits.” - Yuval Shay |

This new simulation-driven layout addresses many of the electromigration (EM) and parasitic challenges of critical circuits and advanced-node designs.

To increase layout automation, the new environment has introduced several techniques for hierarchical floor-planning and planning, along with new placement and routing automation technologies to increase layout design productivity and throughput, and to shorten layout turnaround time.

“We estimate that this layout environment with electrically driven routing and wire editing, real-time design editing, and revolutionary design planning techniques will help to improve productivity by up to 50 per cent,” according to Shay.

“In this market, the winners will be those companies that evolve the fastest - they’re not always the smartest or the richest, but those that re-tool around these new trends and address them the fastest,” Shay concludes.