Microprocessors, FPGAs, DSPs, analogue-to-digital converters (ADCs), and system-on-chip (SoC) devices typically run from multiple voltage rails. To prevent lock-ups, bus contention issues, and high inrush current, designers need these power rails to be started and shutdown in a specific order in a process known as power sequence control or power sequencing.

Some designs may necessitate different sequences, but in any case, proper power-up and power-down sequencing is necessary.

The various power sequencers, monitors and supervisors that have emerged to provide effective ramp up and shutdown have also adopted techniques to monitor voltage and current levels to calculate power levels in protect complex integrated circuits and sub-assemblies.

FPGAs and similar complex ICs are broken down internally into many power domains which require a specific order when starting up or shutting down the device.

The core typically comprises the processor and logic foundation of the FPGA. This domain is characterized by a low voltage and high current power profile. Due to the extremely low voltage, there are very high accuracy requirements, and due to the dynamic nature of the digital load, transient performance must be excellent.

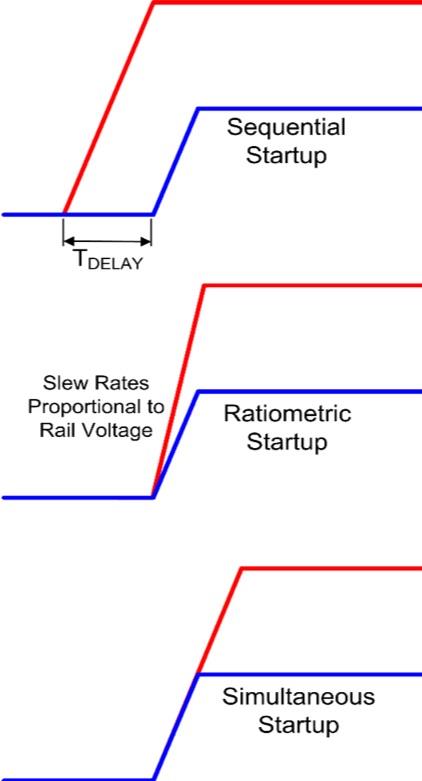

Figure 1: Diagram of three techniques for sequencing power supplies |

Auxiliary circuitry comprises the noise-sensitive analogue circuits in an FPGA, such as phase-locked loops (PLLs) and other analogue circuit elements. Current requirements are reasonably low, but ripple voltage is a major concern and must be minimised to avoid excessive jitter and phase noise in PLLs.

Starting up the power supplies for each domain in the incorrect order can cause problems and can result in damage to the FPGA. Consider that the I/O section is based on transmitting and receiving data on a tristate bus. The I/O control is handled by the core. If the I/O domain is powered on before the core, the I/O pins end in indeterminate states. If the external bus components are powered up, there may be bus contention resulting in high currents in the I/O drivers. As such, the core should be brought up before the I/O domain.

Similarly, devices like power operational amplifiers have two power domains: the analogue and the digital. The digital supplies power to the amplifiers’ diagnostic status flags for over-temperature and overcurrent states and supports the amplifier enable/shutdown functionality. The device specification requires that the digital domain be powered up prior to the analogue supply so that these status flags are functional before the analogue domain is powered on. This is to prevent possible damage to the device.

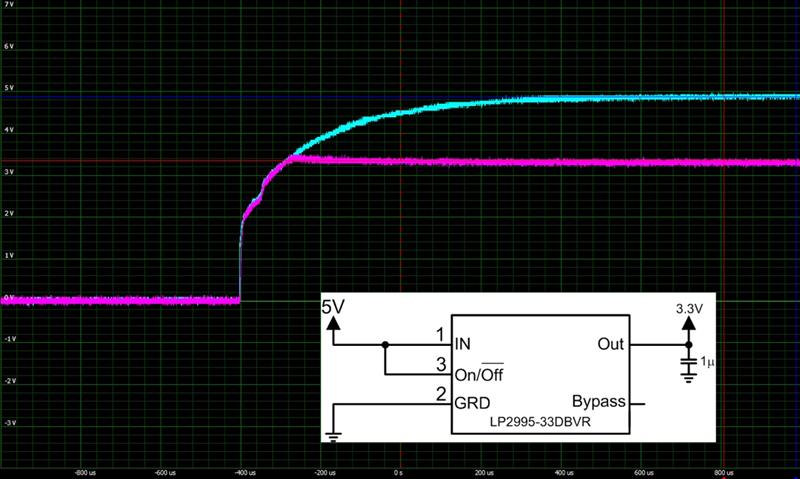

Figure 2: Simultaneous startup of 5 volt and 3.3 volt supplies is accomplished by daisy chaining the regulators. |

Power sequence methodology

There are three common types of multi-rail sequencing (Figure 1). The most common is sequential where one supply rail is turned on first, followed by a delay before the next rail is turned on. The delay is set so that the first rail reaches regulation before the second rail is started.

The second is ratiometric. Here, the rails start up at the same time and reach their rated voltages at the same time. This requires that the rise time of the rails be proportional to the rail voltage in order to achieve regulation at the same time.

Some devices may not tolerate the instantaneous voltage differences occurring before regulation is reached and can lead to the device drawing higher current from one supply during this period.

The third approach, simultaneous startup, minimises instantaneous differences in voltages. A common way of implementing this method is simultaneous power up, in which the voltage rails rise together and at the same rate, with the higher rail, usually the I/O voltage rail, continuing after the lower or core voltage rail has reached its final value.

Regardless of the technique, the voltages must rise monotonically. Failing this, the device may not initialise correctly due to an unexpected drop in the voltage.

A soft start may be applied to limit inrush currents during startup. This practice limits the current during startup, permitting gradual charging of the capacitance of the power rail on startup.

Power supply shutdowns are generally specified to occur in the reverse order from the startup.

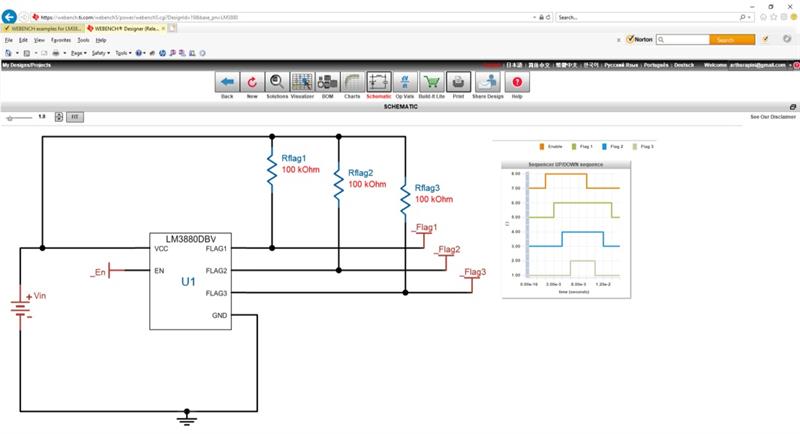

| Figure 3: The WEBENCH Power Designer display for an LM3880 design schematic and chart of the enable input and output flags for controlling external regulators or power supplies. |

Power supply sequencing examples

Simultaneous startup is relatively easy to setup. The highest voltage output is connected to the input(s) of the lower voltage regulator(s) (Figure 2).

In this example the higher voltage is the 5 volt supply. This is fed into the 3.3 volt regulator as well. The 5 volt and 3.3 volt outputs are shown as they rise simultaneously with a minimum voltage difference up to the regulation point of the 3.3 volt supply.

The sequential technique is best implemented using a sequencer integrated circuit e.g. the LM3880 from Texas Instruments. The LM3880 can control multiple independent regulators or power supplies using their enable inputs.

The LM3880, when enabled, will sequentially release its three output flags with individual time delays between the flag. This will permit the connected power supplies to start up. During shutdown the output flags will follow a reverse sequence.

A design example using the LM3880 is shown using TI’s WEBENCH Power Designer software (Figure 3). This free software tool helps the engineer design power related circuits providing schematics, bills of materials, and simulated results. The figure shows the schematic and charts, the enable, and the three flag outputs.

The delay times and sequence order in the LM3880 are fixed, but are factory customisable using the built-in EPROM.

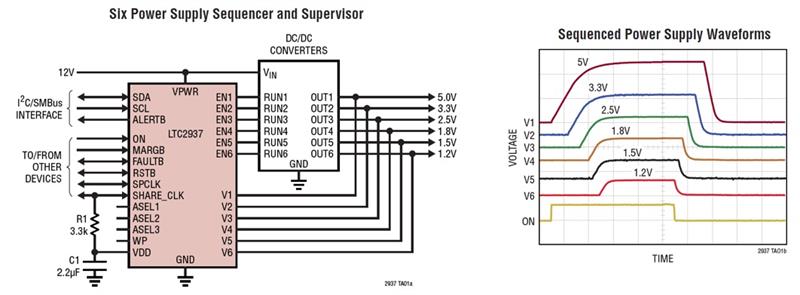

A slightly more sophisticated power control device is the LTC2937 from Analog Devices. Like the LM3880, it can control the order and time delay of up to six power supplies or regulators (Figure 4).

In addition to sequencing up to six power rails, it also monitors the voltages on those rails to detect over voltage, under voltage, drop outs and stalled power startups. In the event of a fault, the device can be programmed to shut down or restart the supplies. Error conditions are logged to internal EEPROM.

The LTC2937 can be programmed and controlled via I2C or SMBus. Programming is supported by Analog’s LTpowerPlay GUI software. The EEPROM allows autonomous operation without software. When a system requires more than six power rails, multiple LTC2937s can be chained together to control as many as 300 supplies.

Figure 4: The LTC2937 can control the sequence of up to six supplies while also monitoring power rail voltages. Multiple devices can be synchronised by a single wire to control up to 300 |

For complex multicore processors, FPGA’s, and other SOC devices, Texas Instruments provides the TPS650860, a configurable multi-rail power management unit.

This single IC, with an input voltage range from 5.6 to 21 volts, contains three step-down controllers, three step-down converters, a sink or source low dropout (LDO) linear regulator, three low voltage input LDOs, regulators, and three load switches.

This device has 13 regulated outputs to supply the needs of the FPGA or other load device.

The buck converters include a built-in power stage, while the buck controllers require an external power stage. Both converters and controllers have integrated voltage sensing inputs to monitor the supply outputs, which can be controlled for sequencing. The load switches include slew rate control, permitting programming of the rails associated with these switches for any of the three sequence types, sequential, ratiometric, or simultaneous.

The TPS650860 is controlled via an I2C interface allowing simple control either by an embedded controller or by an associated SoC manager. This power management IC offers leading-edge control flexibility.

There are multiple methods to control the order of power startup or shutdown varying from very simple to very intricate. These differ in the number of rails controlled, precision, and range of control functions, as well as the cost.